논문 2022-2-18 http://dx.doi.org/10.29056/jsav.2022.12.18

## 동축 구조의 인쇄회로기판을 사용한 테스트 소켓의 S-파라미터 추출

김문정\*\*

# S-parameter Extraction of Test Socket Using Printed Circuit Board with Coaxial Structure

Moonjung Kim\*\*

요 약

다양한 피치(Pitch)와 핀 배열에 대응하기 위해 테스트 소켓의 S-파라미터 분석은 인쇄회로기판을 활용한다. 인쇄회로기판의 기생성분을 제거하기 위해 De-embedding 과정이 필요한 것으로 알려져 있다. 일반적으로 인쇄회로기판의 배선 설계 과정은 마이크로스트립 구조의 전송선을 적용한다. 그러나, 본 논문에서는 동축 구조의 전송선을 사용하여 인쇄회로기판을 설계하고, 테스트 소켓과 인쇄회로기판을 수직 방향으로 조립하여 Test Fixture를 구성한다. 이러한 테스트 소켓과 인쇄회로기판의 수직 조립 방식은 신호 전달 경로가 짧아져서 Fixture의 기생성분을 최소화할 수 있다. 본 논문에서 신호 패드 및 접지 패드 직경, 비아 직경, 인쇄회로기판 두께를 설계하고, 전자장 시뮬레이션을 통해서 S-파라미터를 계산한다. 비아 구조 배치를 통한 인쇄회로기판의 동축 구조 설계와 수직 방향 조립 방식의 Fixture 구조가 테스트 소켓의 S-파라미터 추출 방식으로 활용될 수 있을 것으로 기대한다.

#### Abstract

To cope with various pitches and pin arrangements, S-parameter analysis of test sockets utilizes printed circuit boards. It is known that a de-embedding process is required to remove parasitic components of a printed circuit board. In general, a wiring design process of a printed circuit board applies a transmission line having a microstrip structure. However, in this paper, a printed circuit board is designed using a coaxial transmission line, and a test fixture is constructed by assembling the test socket and the printed circuit boards in the vertical direction. The vertical assembly method of the test socket and the printed circuit boards in this paper can shorten the signal transmission path and minimize the parasitic components of the fixture. In this paper, the diameters of the signal pad, the ground pad, and the via and printed circuit board thickness are designed. The S-parameters are calculated using 3-dimensional electromagnetic field simulation. It is expected that the coaxial structure design of the printed circuit board using the placement of the via structure and the fixture structure of the vertical assembly method can be utilized as an S-parameter extraction method for the test socket.

한글키워드: S-파라미터, 테스트 소켓, 디임베딩, 인쇄회로기판, 픽스처

keywords: S-parameter, Test Socket, De-embedding, Printed Circuit Board, Fixture

\* 공주대학교 전기전자제어공학부 **†** 교신저자: 김문정(email: mjkim@kongju.ac.kr) 접수일자: 2022.12.04. 심사완료: 2022.12.07.

게재확정: 2022.12.20.

#### 1. 서 론

모바일 전자기기의 기술 동향이 고성능화, 다기능화, 소형화로 진행됨에 따라 고성능 반도체제품의 수요가 지속적으로 증가하고 있다. 특히, 반도체제품의 기술이 진화함에 따라 데이터 전송속도가 50Gbps 이상의 수준으로 증가하여 왔다. 이러한 고성능 반도체 소자와 제품을 검사하기 위해서 테스트 소켓은 수많은 미세 피치(Fine Pitch)의 핀과 높은 고주파 성능이 필요하다. 또한, 반도체 테스트 과정에서 테스트 소켓은 다양한 피치와 핀 배열 조건에서 사용된다. 이러한사용 환경 조건으로 인하여 테스트 소켓의 고속동작 성능 평가 과정에서 인쇄회로기판(Printed Circuit Board: PCB)으로 구성한 Fixture가 널리사용되어 왔다.

일반적인 테스트 소켓의 Fixture는 PCB 위에 전송선과 비아를 배치하여 테스트 소켓의 핀들과 전기적으로 연결한다. 전송선을 PCB 평면상에 배치하는 배선 설계 방식은 신호 전달 경로가 길 어지고 PCB 기생성분의 증가를 초래한다. 따라 서 테스트 소켓의 S-파라미터 평가는 반드시 De-embedding 과정이 필요하다. Fixture의 S-파 라미터를 정확히 추출하기 위해서 Thru-Reflect-Line(TRL), Short-Open-Load-Thru (SOLT)와 같은 De-embedding 방식이 보고되었 다[1-2]. 이러한 방식은 Fixture 영향을 제거하여 테스트 소켓만의 S-파라미터를 추출할 수 있다. 그러나, 정밀한 표준 시료를 사용하여 여러 번의 Fixture 특성 평가 과정이 필요하다. Automatic Fixture Removal (AFR), Smart Fixture De-embedding(SFD), In-Situ De-embedding (ISD)과 같은 2X-Thru De-embedding 방식은 표준 구조의 시료를 사용하고 높은 정확성을 확 보한 것으로 알려져 있다[3-5]. 그러나 TRL, SOLT, 2X-Thru 방식은 테스트 소켓 평가 과정

에서 PCB 위에 패턴을 배치하고 이를 테스트 소 켓에 연결하기 때문에 일정 이상의 배선 길이가 필요하다. 이러한 불가피한 배선 설계로 인해서 PCB 크기와 기생성분이 증가하게 된다.

본 논문은 동축 구조의 전송선을 채택하여 PCB를 설계하고 테스트 소켓과 수직 방향으로 조립하여 Fixture를 구성한다. 이러한 방식은 PCB와 테스트 소켓 사이의 신호 전달 경로가 짧아져서 Fixture의 기생성분을 줄일 수 있다. 또한, S-파라미터 De-embedding 과정의 정확성을 개선할 수 있다.

#### 2. 테스트 소켓의 Fixture 설계

테스트 소켓은 반도체 소자 및 제품의 평가를 위해 사용하며, 수많은 금속 소재의 접촉 핀 (Contact Pin)과 절연 소재의 하우징(Housing)으로 구성한다. 반도체 제품의 동작 속도가 지속적으로 증가함에 따라 테스트 소켓도 우수한 고주파 성능을 요구하고 있다. 테스트 소켓은 다양한 피치와 핀 배열에 대응할 수 있도록 설계한다. 핀 피치와 배열에 따라 테스트 소켓의 특성 임피던스가 변하게 되고 이는 고주파 성능의 변화를 초래한다[6]. 따라서 본 논문은 Pogo Pin 구조, 0.75mm 피치, Ground-Signal-Ground 배치의 핀배열을 가지는 테스트 소켓을 대상으로 PCB 기반의 Fixture 설계와 3차원 전자장 시뮬레이션을수행한다.

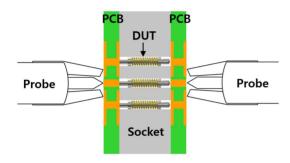

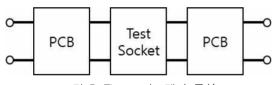

그림 1은 PCB와 테스트 소켓으로 구성된 Fixture의 단면 구조를 보여주고 있다. Vector Network Analyzer를 사용한 S-파라미터 측정을 위해서 Fixture는 Probe를 통해 전기적으로 연결된다. Probe는 중앙의 신호 단자(Signal Tip)를 양쪽의 접지 단자(Ground Tip)가 둘러싸고 있으며, 단자는 일렬 배치로 구성된다. 테스트 소켓

내부는 3개의 접촉 핀이 실장되어 있고, 이 또한 일렬 형태로 배치되어 있다. De-embedding 방식의 정확성을 향상시키기 위해서는 Fixture 내의신호 경로를 최소화하여야 한다. 본 논문에서 PCB와 테스트 소켓을 수직 방향을 쌓아서 조립하는 방식을 적용하여 신호 경로를 줄이고 Fixture의 기생성분을 최소화한다. 또한, PCB 설계에서 동축 구조를 구현하기 위해서 패드와 비아를 배치하였다. 그림 1에서 볼 수 있듯이, 접촉 핀은 위와 아래 PCB에 물리적으로 접촉하여 전기적으로 연결된다.

그림 1. PCB와 테스트 소켓의 수직 조립 방식을 적용한 Fixture의 단면 구조

Fig. 1. Cross-sectional structure of a test socket fixture applying the vertical assembly method of PCB and test socket

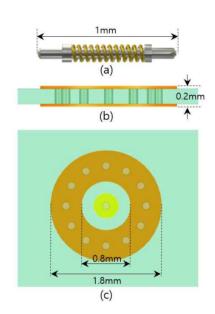

본 논문의 테스트 소켓 Fixture의 구성 부품과 구조는 그림 2에 나타나 있다. 그림 2 (a)는 테스트 소켓에 삽입되는 접촉 핀을 보여주고 있으며, 본 논문에서 핀의 길이는 1.0mm로 결정하였다. PCB 두께는 Fixture의 신호 경로 최소화를 고려하여 0.2mm로 선정하였으며, 따라서 Fixture 두께는 1.4mm를 가진다. 그림 2 (b)는 PCB의 단면 구조를 보여주고 있다. PCB는 2층 금속 구조를 가지며, 위와 아래 구리 패드의 두께는 35um이며, 비아를 통해 전기적으로 연결되어 있다. 위와 아래

에 있는 신호 패드와 접지 패드의 설계는 동일하다. 그림 2 (b)에서 PCB 내부에 배치한 신호 비아와 접지 비아를 볼 수 있다. 그림 2 (c)는 PCB위에 배치된 동축 구조의 패턴 설계를 보여주고있다. 중앙의 원과 외측 원은 각각 신호 패드(Signal Pad)와 접지 패드(Ground Pad)에 해당한다. 동축 구조를 구현하기 위해서 접지 패드에일정한 간격으로 비아를 둘러 가면서 배치하였다. 비아 개수는 동축 구조에서 전자기장의 유효한 분포 범위와 PCB제조 공정을 고려하여 12개로 결정하였다. 신호 패드 직경과 비아 직경은각각 0.4mm, 0.12mm으로 설계하였다. 또한, 접지 패드 내부 직경과 외부 직경은 각각 0.8mm, 1.8mm로 설정하였다.

그림 2. 테스트 소켓 Fixture의 구성 부품과 구조: (a) 테스트 소켓의 접촉 핀, (b) PCB의 단면 구조, (c) PCB의 평면도

Fig. 2. Components and structure of test socket fixture: (a) contact pin of test socket, (b) cross-sectional structure of PCB, (c) top view of PCB

### 3. 테스트 소켓 Fixture 분석

PCB, 테스트 소켓 및 Fixture의 3차원 전자기 장 시뮬레이션은 ANSYS HFSS를 사용하였으며, S-파라미터는 40GHz까지 계산하였다. PCB, 테스트 소켓, Fixture는 모두 동일한 포트(Port) 지정과 배치를 가지도록 설정하였다.

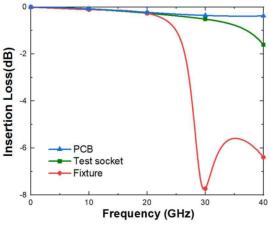

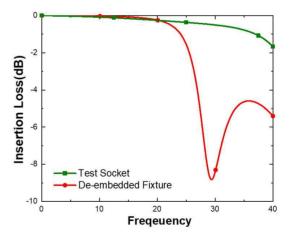

그림 3은 PCB, 테스트 소켓, Fixture의 삽입손실(Insertion Loss)을 보여주고 있다. PCB는 임피던스 매칭 설계와 얇은 두께로 인하여 매우 우수한 삽입손실을 확보하고 있다. 이러한 삽입손실 결과는 매우 얇으면서 우수한 손실 특성을 가진 본연구의 PCB가 Fixture로써 활용할 수 있음을 의미한다. 테스트 소켓은 임피던스 매칭 기반 설계와비교적 짧은 접촉 핀 길이로 인하여 -1dB 삽입손실 주파수가 대략 37GHz에 해당하는 우수한 특성을 가진다. 반면에 그림 3의 PCB-Test Socket-PCB 순서로 구성된 Fixture는 23GHz 이후 매우높은 손실 특성을 가지며, PCB와 테스트 소켓과다른 경향을 보인다. 이러한 결과 차이는 접촉 핀,신호 패드 및 접지 패드 사이의 전자기적 결합(Electromagnetic Coupling)이 원인으로 보인다.

그림 3. PCB, 테스트 소켓 및 Fixture의 삽입손실 Fig. 3. Insertion loss of PCB, test socket, and fixture

그림 4. PCB, 테스트 소켓 및 Fixture의 반사손실 Fig. 4. Reflection loss of PCB, test socket, and fixture

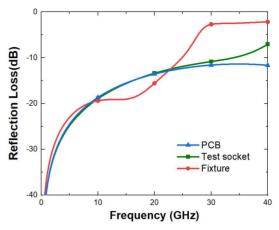

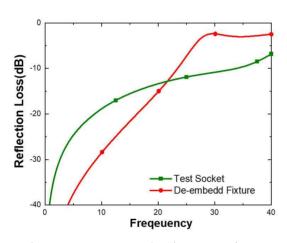

그림 4는 PCB, 테스트 소켓, Fixture의 반사손실(Reflection Loss)을 보여주고 있다. PCB와 테스트 소켓은 매우 우수한 반사손실을 확보하고 있다. 30GHz 이후 PCB와 테스트 소켓의 차이는 두께 차이와 임피던스 매칭 정도에 의해 결정된 것이다. PCB의 우수한 반사손실 결과는 40GHz까지 Fixture로써 활용할 수 있음을 의미한다. Fixture는 23GHz 전까지는 우수한 반사손실 특성을 보이지만, 23GHz 이후 급격히 반사손실 특성이 저하되고 있다. 접촉 핀, 신호 패드 및 접지패드 간의 전자기장 분포(Electromagnetic Field Density) 분석을 통해 원인 추정이 가능할 것으로 예상한다.

그림 3과 그림 4에서 볼 수 있듯이 PCB의 삽입손실과 반사손실은 40GHz 대역까지 우수한 주파수 특성을 확보하고 있다. 이러한 성능 결과는 Fixture의 기생성분을 최소화하기 위한 0.2 mm두께의 PCB 설계와 임피던스 매칭 기반의 동축구조 설계에 기인한다.

그림 5에서 보듯이 본 논문의 Fixture는 PCB, Test Socket, PCB 순서로 직렬 연결되어 있다. Test Socket에 연결하는 PCB는 동일한 구조와 전기적 특성을 가진다. 일반적으로 직렬 연결한 Fixture의 전체 시스템 특성은 T-파라미터를 사용하여 계산할 수 있다. 즉, PCB와 Test Socket 각각의 T-파라미터 정보가 있으면, Fixture의 T-파라미터는 아래와 같은 수식으로 표현한다 [7].

$$T_{Fixture} = T_{PCB}T_{TestSocket}T_{PCB} \tag{1}$$

$$T_{Test,Socket} = (T_{PCB})^{-1} T_{Fixture} (T_{PCB})^{-1}$$

(2)

여기서  $T_{Fixture}$ 는 전체 시스템의 T-파라미터에 해당하고,  $T_{PCB}$ 는 PCB의 T-파라미터를 의미하고,  $T_{TestSocket}$ 는 테스트 소켓의 T-파라미터에 해당한다. 테스트 소켓의 T-파라미터는 수식 (2)의 연산을 통해 계산할 수 있다. 또한, T-파라미터는 수식 계산을 통해 S-파라미터로 변환할 수 있다.

그림 5. Fixture 시스템의 구성 Fig. 5. Composition of fixture system

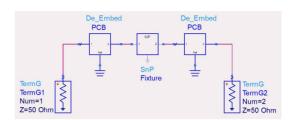

그림 6은 테스트 소켓의 S-파라미터 De-embedding 회로를 보여준다. Keysight ADS 는 직렬 연결 구조의 시스템에서 Device Under Test(DUT)의 S-파라미터를 De-embedding하여 데이터를 추출할 수 있다. 그림 6의 회로에서 중 앙의 Fixture 기호는 PCB-Test Socket-PCB로 구성된 전체 시스템의 S-파라미터를 의미한다. 또한, Fixture 양단의 De-embed 기호는 Fixture 에서 De-embedding 하는 PCB의 S-파라미터를 의미한다. 즉, 그림 6의 회로는 Fixture에서 양쪽 의 PCB를 De-embedding 하여 Test Socket의 S-파라미터를 추출하는 기능을 수행한다.

그림 6. 테스트 소켓의 S-파라미터 De-embedding 회로

Fig. 6. S-parameter de-embedding circuit of test socket

그림 7은 Keysight ADS를 사용하여 Fixture 에서 PCB 성분을 제거하는 De-embedding 완료한 Fixture의 삽입손실을 보여준다. PCB 영향이 제거된 Fixture, 즉 테스트 소켓의 삽입손실에서 -1dB 삽입손실 주파수는 24GHz에 도달한다. 반면에 ANSYS HFSS를 사용하여 테스트 소켓의 S-파라미터 시뮬레이션을 수행한 결과, 테스트 소켓의 -1dB 삽입손실 주파수는 37GHz에 해당한다. 그림 7에서 보듯이 주파수 대역이 20GHz까지 테스트 소켓과 De-embedding 완료한Fixture의 삽입손실은 유사한 수준과 경향을 보임을 알 수 있다. 그러나 주파수 대역이 20GHz

그림 7. De-embedding 완료한 Fixture와 Test Socket의 삽입손실

Fig. 7. Insertion loss of de-embedded fixture and test socket

이후부터 테스트 소켓과 De-embedding 완료한 Fixture의 삽입손실은 서로 다른 경향을 보인다. Fixture 전체 시스템에서 PCB의 영향이 제거되었기 때문에 전체 주파수 대역에서 테스트 소켓과 De-embedding 완료한 Fixture는 유사한 삽입손실 결과를 가질 것으로 예상하였지만, 그림 7의 삽입손실 결과는 테스트 소켓과 PCB 간의 추가적인 요인에 의한 영향이 있음을 보여준다.

그림 8은 Fixture 전체 시스템에서 PCB 성분을 제거한 Fixture의 반사손실을 보여준다. PCB 영향이 제거된 Fixture, 즉 테스트 소켓의 반사손실에서 -10dB 반사손실 주파수는 23GHz에 해당한다. 반면에 ANSYS HFSS를 사용하여 테스트소켓의 S-파라미터 시뮬레이션을 수행한 결과,테스트 소켓의 -10dB 반사손실 주파수는 33GHz에 해당한다.

그림 8. De-embedding 완료한 Fixture와 Tes Socket의 반사손실

Fig. 8. Reflection loss of de-embedded fixture and test socket

그림 8에서 보듯이 주파수 대역이 21GHz까지 De-embedding 완료한 Fixture의 반사손실이 테스트 소켓보다 상당히 낮은 반사손실 경향을 보인다. 그림 7에서 보듯이 주파수 대역 20GHz 이

내에서 De-embedding 완료한 Fixture의 낮은 반사손실 특성은 테스트 소켓보다 다소 우수한 삽입손실 결과를 초래한다. 그러나 주파수 대역이 21GHz 이후부터 테스트 소켓의 반사손실이 더낮은 값을 보이지만, De-embedding 완료한 Fixture의 반사손실은 급격한 손실 증가로 인해서 높은 주파수 대역에서 큰 값을 가진다. 이러한 급격한 손실 증가는 29GHz에서 발생한 반사손실의 공진 특성으로 발생한 결과이다. 또한, 그림 7의 삽입손실 결과에서 보듯이 동일한 29GHz의 공진 특성으로 인해 삽입손실 특성이 급격히 저하된다. 따라서 De-embedding 완료한 Fixture와 테스트 소켓의 S-파라미터 차이는 29GHz의 공진 특성과 밀접한 원인 관계가 있음을 알 수있다.

#### 4. 결 론

본 논문은 테스트 소켓의 S-파라미터 추출을 위해 Fixture를 설계하고 시뮬레이션하였다. 동축 구조를 채택하여 PCB를 설계하고 테스트 소켓과 수직 방향으로 조립하여 Fixture를 구성하였다. 이러한 방식은 PCB와 테스트 소켓 사이의신호 경로가 짧아져서 Fixture의 기생성분을 줄일 수 있다. 또한, S-파라미터 De-embedding 과정의 정확성을 개선할 수 있다. 본 논문에서 PCB, 테스트 소켓 및 Fixture의 삽입손실과 반사손실을 계산하고 분석하였다. 본 연구의 우수한 PCB 고주과 성능은 Fixture 기생성분을 최소화하기 위한 PCB 두께 설계와 임피던스 매칭 기반의 동축 구조 설계에 기인하며, PCB가 S-파라미터 추출을 위한 Fixture로써 활용할 수 있음을 의미한다.

직렬 연결 구조의 Fixture에서 PCB 영향을 제 거하기 위해 S-파라미터 De-embedding을 수행 하였다. 전체 시스템에서 PCB 영향이 제거로 인해 테스트 소켓과 De-embedding 완료한 Fixture 는 유사한 삽입손실 결과를 가질 것으로 예상하였다. 그러나 테스트 소켓과 PCB 간의 추가적인 요인에 의한 영향이 있음을 확인하였다. 또한, De-embedding 완료한 Fixture와 테스트 소켓의 S-파라미터 차이는 29GHz의 공진 특성과 밀접한 원인 관계가 있음을 확인하였고 추가적인 연구를 통해 원인을 규명하고자 한다.

#### Acknowledgement

이 성과는 정부(과학기술정보통신부)의 재원으로 한국연구재단의 지원을 받아 수행된연구임(No. 2021R1F1A1062192).

#### 참고문 헌

- [1] G. F. Engen and C. A. Hoer. (1979). Thru-Reflect-line: An improved technique for calibrating the dual six-port automatic network analyzer. IEEE Trans. Microw. Theory Techn., MTT-27(12), 987 993.DOI: https://doi.org/10.1109/TMTT.1979.1129778

- [2] L. Galatro, A. Pawlak, M. Schroter, and M. Spirito. (2017). Capacitively loaded inverted CPWs for distributed TRL-based de-embedding at (sub) mm-waves. IEEE Trans. Microw. Theory Techn., 65(12), 4914 - 4924, DOI:

- https://doi.org/110.1109/TMTT.2017.2727498

- [3] B. Chen, X. Ye, B. Samaras, and J. Fan. (2015). A novel de-embedding methodsuitable for transmission-line measurement. Proc. Asia-Pac. Symp. Electromagn. Compat.. (pp.1 4), Taipei. DOI: https://doi.org/10.1109/APEMC.2015.7175313

- [4] C. Wu, B. Chen, T. Mikheil, J. Fan, and X. Ye. (2017). Error bounds analysis of de-embedded results in 2x thru de-embedding methods. Proc. IEEE Int. Symp. Electromagn. Compat. Signal/Power Integrity. (pp. 532 536). DOI: https://doi.org/10.1109/ISEMC.2017.8077927

- [5] Y. Chen, B. Chen, J. He, R. Zai, J. Fan, and J. Drewniak. (2018). De-embedding comparisons of 1X-reflect SFD, 1-port AFR, and 2X-thru SFD. Proc. IEEE Asia-Pac. Symp. Electromagn. Compat.. (pp. 160 164). DOI:

- https://doi.org/10.1109/ISEMC.2018.8393759

- [6] M. Kim. (2019). Analysis of Electrical Performance on Probe Pin. Journal of Software Assessment and Valuation, 1. 109–114. DOI:

- https://dx.doi.org/10.29056/jsav.2019.06.13

- [7] H. Barnes and J. Moreira. (2017). Verifying the accuracy of 2x-Thru de-embedding for unsymmetrical test fixtures. IEEE Conference on Electrical Performance of Electronic Packaging and Systems. DOI: https://dx.doi.org/10.1109/EPEPS.2017.8329760

저 자 소 개

김문정(Moonjung Kim)

1997.2 경북대학교 전자공학과 학사 1999.2 한국과학기술원 전기 및 전자공학과 석사 2003.8 한국과학기술원 전기 및 전자공학과 박사 2006.9-현재 공주대학교 전기전자제어공학부 교수 <주관심분야> 신호무결성, 전원무결성